Che cos’è PCI Express? Come funziona?

PCI Express è una tecnologia che vediamo sempre ovunque. Si sta sviluppando sempre di più ogni giorno. Di conseguenza, è anche oggetto di cronaca ed è nelle nostre vite da 20 anni. Questa tecnologia, che dall’esterno non mostra segni di cambiamento, deve avere qualcosa di speciale per essere utilizzata per così tanto tempo.

Se ti stai chiedendo cosa faccia esattamente e come PCI Express sia rimasto una parte essenziale di ogni computer in casa, in ufficio e negli angoli per due decenni, sei nel posto giusto.

Prima del PCI Express

Torniamo agli anni ’80, quando le schede madri dei computer erano adornate con un sacco di strani slot per bus da equipaggiare con dozzine di chip e schede extra. Ricordi il bus ISA di IBM? Questo bus, che sta per Industry Standard Architecture, aveva preso il suo posto in ogni computer, anche se non ebbe molto successo rispetto agli sviluppi della tecnologia.

Con l’avanzare del decennio successivo, processori più veloci hanno aumentato la necessità di bus dalle prestazioni migliori. Di conseguenza, sono emersi due nuovi percorsi di dati. Il bus PCI e il bus VLB (VESA Local Bus) sono stati prodotti da Intel. Entrambi sono stati rilasciati nel 1992.

Poiché il PCI era stato originariamente progettato per funzionare a 33 MHz, sembrava più lento rispetto agli altri due rivali. In risposta, il VLB ha funzionato allo stesso clock del bus frontale (FSB) della CPU, consentendo al VLB di raggiungere 40 o 50 MHz a seconda del processore centrale. Oh, a proposito, anche se il PCI è stato successivamente rivisto per raggiungere i 66 MHz, nessun computer lo supportava davvero.

Sebbene VLB fosse buono, carino, bello, non è stato sempre in grado di sostenere questa performance in modo coerente. Aveva una latenza peggiore del PCI. Lo slot VLB era anche molto più grande del PCI. Nonostante questi vantaggi, PCI ha impiegato del tempo per guadagnare terreno nel settore delle schede madri, in particolare nei mercati delle workstation e dei server.

A quel tempo, i normali utenti di computer di solito non avevano molte schede di espansione o richieste significative sui bus. Ma la situazione è cambiata quando l’industria delle schede grafiche 3D era in aumento e le migliori schede avevano connettori PCI. La gente ha iniziato a preferire i nuovi bus della scheda madre. Man mano che la potenza di questi acceleratori grafici aumentava ei giochi usavano quella potenza, i limiti del bus PCI divennero chiari.

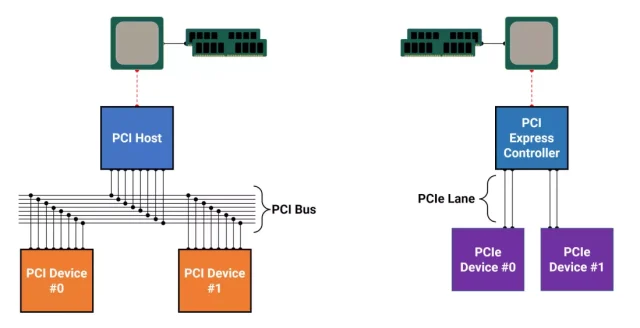

Come i bus ISA e VLB precedenti, PCI era un bus parallelo. Ciò significava che tutte le schede negli slot di espansione PCI utilizzavano lo stesso bus e dovevano alternarsi per inviare e ricevere dati. Questo potrebbe essere un problema per le schede video perché sebbene possano utilizzare facilmente il bus, non potrebbero eseguire un’elaborazione rapida. Intel ha risolto questo problema nel 1997 producendo l’Accelerated Graphics Port (AGP), un bus PCI dedicato per la scheda grafica.

Così finì un millennio e ne iniziò un altro. Gli utenti iniziarono a richiedere un autobus ancora più veloce. Poco dopo aver introdotto il bus PCI, Intel ha formato uno Special Interest Group (PCI-SIG) per assistere i fornitori di schede madri e schede di espansione nel garantire che il loro hardware sia conforme alle potenziali specifiche. All’inizio degli anni 2000, questo gruppo era composto da centinaia di membri. Cinque di questi membri (Compaq, Dell, HP, IBM e Microsoft) hanno collaborato con Intel su un nuovo prodotto per sostituire PCI.

PCI-SIG, nome in codice 3GIO (3rd Generation I/O), ha annunciato i frutti del suo lavoro nell’aprile 2002 e ha introdotto la sua nuova tecnologia come PCI Express.

PCI contro PCI Express

Sebbene condividano lo stesso nome, i bus PCI Express (chiamati anche PCIe) e PCI hanno poco in comune. La differenza fondamentale è che il sistema PCIe è point-to-point. Un dispositivo utilizza un solo bus e non lo condivide con nient’altro. Mentre PCIe può sembrare un miglioramento di AGP, c’è anche una differenza significativa nel modo in cui i dati vengono trasmessi.

PCI e AGP utilizzano la comunicazione dati parallela inviando e ricevendo più bit di dati contemporaneamente, mentre PCIe fornisce la comunicazione dati seriale inviando solo un bit per loop. Questo approccio elimina il problema del disallineamento dell’orologio che può verificarsi con la comunicazione parallela e in ultima analisi consente a PCIe di funzionare a velocità di clock molto più elevate.

Il limite assoluto di PCI è 66 MHz. Una sua versione ulteriormente ampliata, PCI-X, può raggiungere i 533 MHz, mentre la velocità di clock più lenta per PCI Express è di ben 1250 MHz.

Questa velocità è stata raggiunta attraverso l’uso di flash differenziali a bassa tensione (LVDS), un doppio segnale sfasato di 180 gradi operante a una frazione della tensione utilizzata da PCI e AGP.

La natura seriale di PCI Express ha inoltre notevolmente ridotto il numero di cavi/tracce necessari per il trasferimento dei dati. PCI ne richiedeva 32 e PCIe solo quattro cavi. Sebbene tecnicamente ne fossero richiesti solo due, uno per ogni flash, PCI Express era completamente bidirezionale, inviando informazioni in entrambe le direzioni contemporaneamente, quindi utilizzava sempre una coppia di set di flash accoppiati.

Questo gruppo a quattro fili è più comunemente noto come corsie PCIe e indica il numero di corsie utilizzate tramite un moltiplicatore. Ad esempio, x1 è una striscia, x4 è quattro strisce, x16 è sedici strisce.

Con il modo in cui funziona il sistema LVDS, un bus PCIe a corsia singola può trasmettere dati a una velocità minima di 200 MB/s in una direzione. Dovrebbe essere ancora più alto di quello sulla carta. Tuttavia, le informazioni trasmesse vengono codificate e inviate in pacchetti a 8 bit, con ogni pacchetto sequenziale inviato in una corsia sequenziale. Di conseguenza, la velocità dati effettiva è sempre inferiore a causa dei bit aggiuntivi richiesti per la codifica.

La combinazione di comunicazione seriale e trasferimento dati basato su pacchetto significa anche che i relativamente pochi pin nella connessione dello slot sono più che sufficienti per gestire tutto. Il numero minimo di pin richiesti per qualsiasi dispositivo PCI Express è 18. Tuttavia, non è necessario utilizzarli tutti. Al contrario, gli slot PCI richiedono almeno 56 pin, che inevitabilmente occupano più spazio, non importa quanto siano disposti in modo compatto.

Tuttavia, uno slot PCIe x16 è notevolmente più lungo di qualsiasi slot PCI o AGP standard. Infatti, indipendentemente dalla lunghezza dello slot di espansione PCI Express, sono quasi tutti della stessa larghezza e altezza, con slot più lunghi che hanno più corsie per inviare il traffico. Tutto ciò che riguarda l’alimentazione e la gestione del sistema si trova nella prima parte dello slot, poco prima del notch in plastica.

Le domande per PCI Express devono essere universali

PCIe è stato creato fin dall’inizio della sua progettazione con l’obiettivo di espandere il più possibile le sue aree di utilizzo. A tal fine, gli ingegneri hanno reso il sistema retrocompatibile con PCI solo in termini di software. In questo modo, gli sviluppatori non dovevano preoccuparsi di riscrivere il proprio software per riconoscere e accedere ai dispositivi utilizzando il bus PCI Express, almeno in teoria.

Per ottenere il massimo dal nuovo sistema, le aziende produttrici di hardware hanno progettato i loro prodotti per adattare completamente PCI Express a vari componenti e strutture. Sebbene ci siano voluti più di un decennio per raggiungere questo obiettivo, alla fine è diventato disponibile il bus universale ad alta velocità per collegare la CPU al resto della scheda madre e a tutti gli slot per schede di espansione.

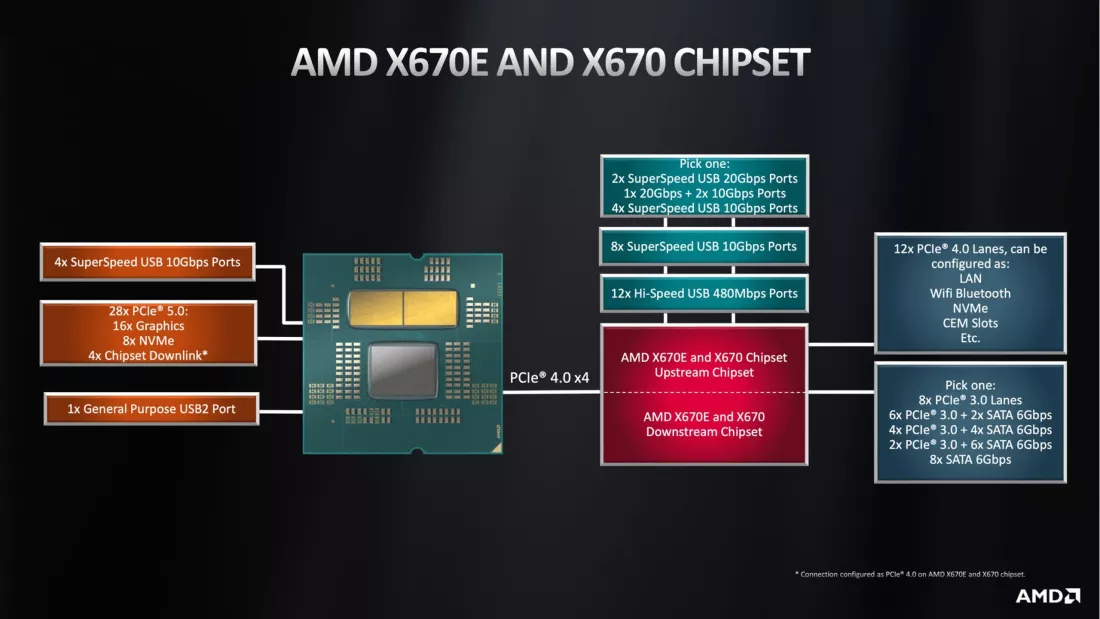

Scegli oggi qualsiasi CPU o scheda madre di AMD e Intel e il processore e Southbridge hanno grandi controller PCI Express con più corsie. Ad esempio, il processore Ryzen 9 7950X di AMD e il chip della scheda madre X670E hanno rispettivamente 28 e 20 corsie PCIe. Nel caso della CPU Ryzen, sono divisi in ruoli specifici: 16 per lo slot della scheda video, 8 per le due unità di archiviazione e i restanti 4 per la comunicazione con la scheda madre. Tuttavia, le corsie sul chip X670E possono essere utilizzate in vari scenari di dati come adattatori Ethernet, Wi-Fi e Bluetooth.

Come è nato il PCI Express oggi?

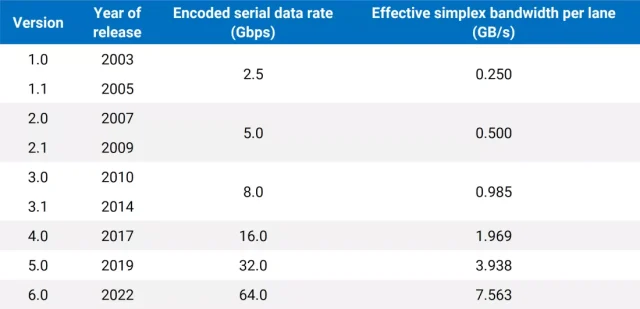

Con l’aumentare della domanda, PCI Express è stato regolarmente aggiornato dal suo lancio per tenere il passo con i requisiti di larghezza di banda. Un’importante restrizione sugli aggiornamenti era il requisito della piena compatibilità con le versioni precedenti. Ad esempio, un dispositivo PCIe 3.0 dovrebbe essere in grado di funzionare anche in uno slot PCIe 5.0. Tuttavia, questo ha creato alcuni problemi.

PCI-SIG ha rilasciato otto aggiornamenti con revisioni importanti contenenti miglioramenti rispetto al rilascio iniziale nel 2003. Durante lo sviluppo di ogni revisione, i membri rilevanti di PCI-SIG stavano conducendo studi di fattibilità per determinare quali velocità e caratteristiche potevano essere realisticamente prodotte, cercando di mantenere bassi i costi. Ad esempio, nella versione 3.0, invece di raddoppiare la velocità di clock dei flash come nella versione precedente, è stata aumentata solo del 60%.

Allora perché i computer stanno appena iniziando ad adottare PCIe 4.0 e 5.0 anche se è passato molto tempo da quando sono usciti?

Si riduce a questioni di necessità e costo. In questo momento i computer hanno una larghezza di banda più che sufficiente per spostare i dati internamente e non c’è motivo per cui un utente normale diverso dai giocatori abbia bisogno di PCIe 6.0. Ma nel mondo dei server, i progettisti di sistemi utilizzeranno felicemente tutta la larghezza di banda possibile.

Cosa promette PCI Express per il futuro?

Con la versione 7.0 prevista per il rilascio nel 2025, PCI-SIG non sta facendo alcuna mossa per rallentare lo sviluppo della tecnologia o sostituirla con qualcosa di diverso. La velocità di trasferimento dei dati dovrebbe raddoppiare nel prossimo aggiornamento. Tuttavia, se i membri del gruppo pensano che salire a 128 Gbps non abbia senso dal punto di vista finanziario, potremmo vedere la velocità a livelli leggermente inferiori.

Quindi, figuriamoci provare nuove funzionalità, dato l’attuale tasso di adozione di PCIe 5.0, gli utenti normali non saranno in grado di vedere queste velocità per molti anni, forse fino alla metà degli anni ’30.